cpld编程语言 FPGA和CPLD的区别,你知道吗?(上)

2021-08-17

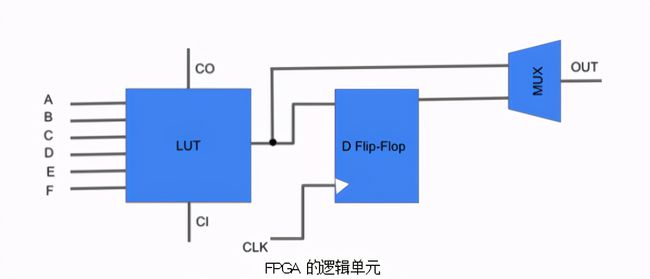

1、FPGA(-Gate),现场可编程门阵列,是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它作为专用集成电路(ASIC)领域的一种半定制电路应运而生,既解决了定制电路的不足,又克服了原有可编程器件门电路数量有限的缺点。

2、CPLD() 复杂可编程逻辑器件是从 PAL 和 GAL 器件发展而来的器件。它们规模较大,结构复杂,属于大规模集成电路的范畴。它是用户根据自己的需要构造逻辑功能的数字集成电路。基本设计方法是利用集成开发软件平台cpld编程语言,利用原理图、硬件描述语言等方法生成相应的目标文件,通过下载线将代码传输到目标芯片(“在系统”编程)实现设计的数字系统。

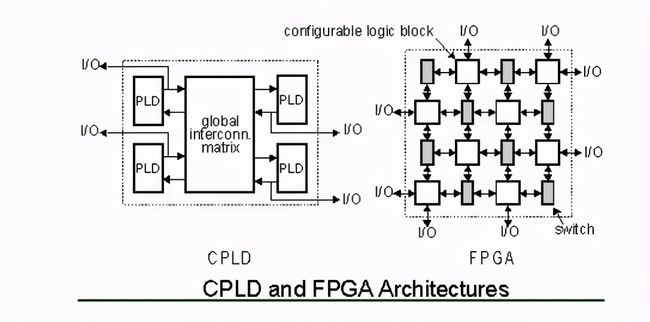

3、FPGA 与 CPLD 的区别:

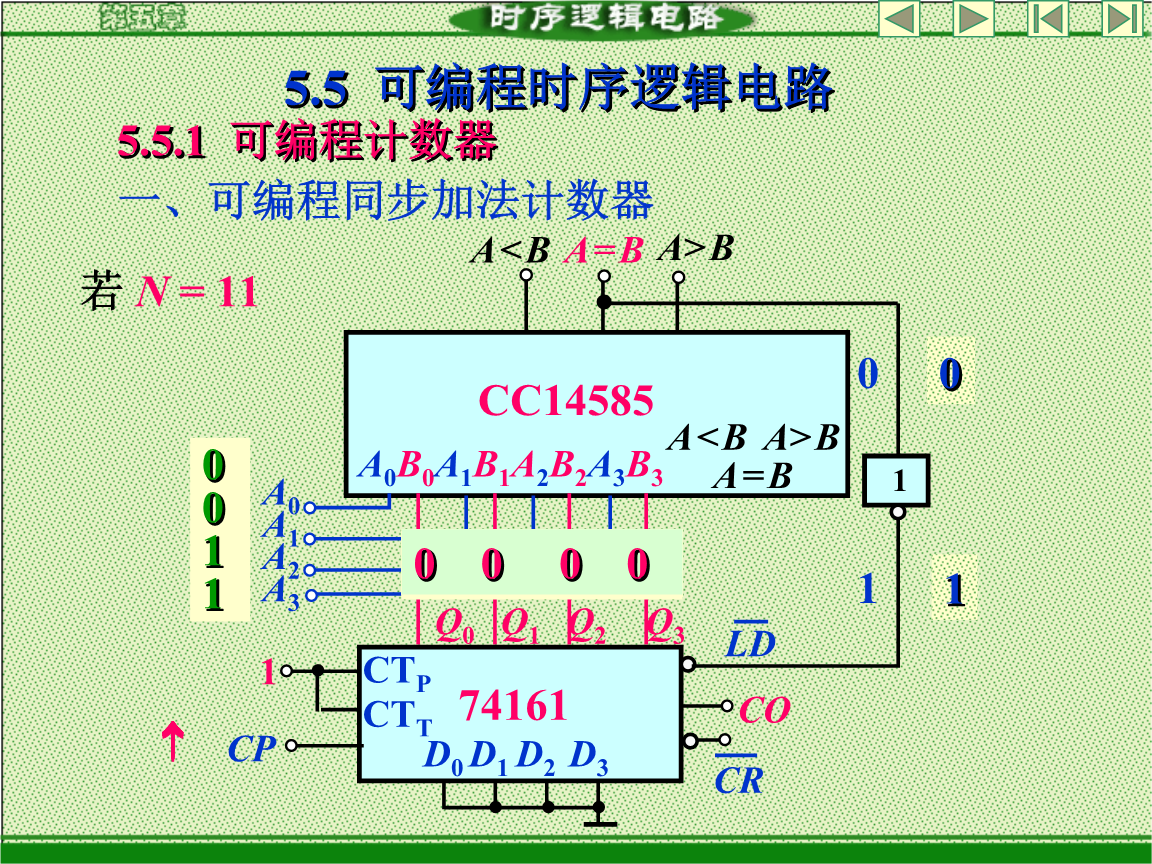

①CPLD更适合完成各种算法和组合逻辑,FPGA更适合完成时序逻辑。也就是说,FPGA更适合触发器丰富的结构,CPLD更适合触发器有限、乘积项丰富的结构。

②CPLD的连续布线结构决定了其时序延迟的均匀性和可预测性,而FPGA的分段布线结构决定了其延迟的不可预测性。

③ FPGA在编程上比CPLD具有更大的灵活性。 CPLD通过修改具有固定互连电路的逻辑功能进行编程,FPGA主要通过改变内部布线的布线进行编程; FPGA可以在逻辑门下编程,CPLD在逻辑块下编程。

④FPGA的集成度高于CPLDcpld编程语言,布线结构和逻辑实现更复杂。

⑤CPLD比FPGA更方便使用。 CPLD的编程采用或技术,不需要外部存储芯片,使用简单。并且FPGA的编程信息需要存储在外部存储器中,使用方法复杂。

⑥CPLD比FPGA快,时间可预测性更强。这是因为FPGA是门级编程,CLB之间分布式互连,而CPLD是逻辑块级编程,其逻辑块之间的互连是集总的。

⑦在编程方式上,CPLD以或存储器编程为主,编程次数可达次。优点是系统断电时,编程信息不会丢失。 CPLD 可分为在编程器上编程和在系统编程。大多数FPGA基于SRAM编程,系统断电时编程信息丢失。每次上电时,都需要从器件外部将编程数据重新写入SRAM中。其优点是可任意编程次数,工作时可快速编程,实现板级和系统级动态配置。

⑧CPLD保密性好,FPGA保密性差。

⑨一般情况下,CPLD的功耗比FPGA大,集成度越高越明显。

随着复杂可编程逻辑器件 (CPLD) 密度的增加,数字器件的设计人员既灵活又易于进行大规模设计,产品可以快速进入市场。许多设计人员已经感觉到 CPLD 易于使用。可预测的时序和高速的优点,然而,过去由于CPLD密度的限制,他们不得不转向FPGA和ASIC。现在,设计人员可以体会到密度高达数十万门的 CPLD 的好处。